产品中心

PRODUCT

电 话:0898-08980898

手 机:13877778888

联系人:xxx

E_mail:admin@Your website.com

地 址:广东省清远市

【干货】一文带你搞懂JK触发器工作原理+逻辑功能+真值表总结

触发器是一种边沿触发触发器,意味着只有当时钟脉冲施加到其时钟输入时,它的输出才会改变。

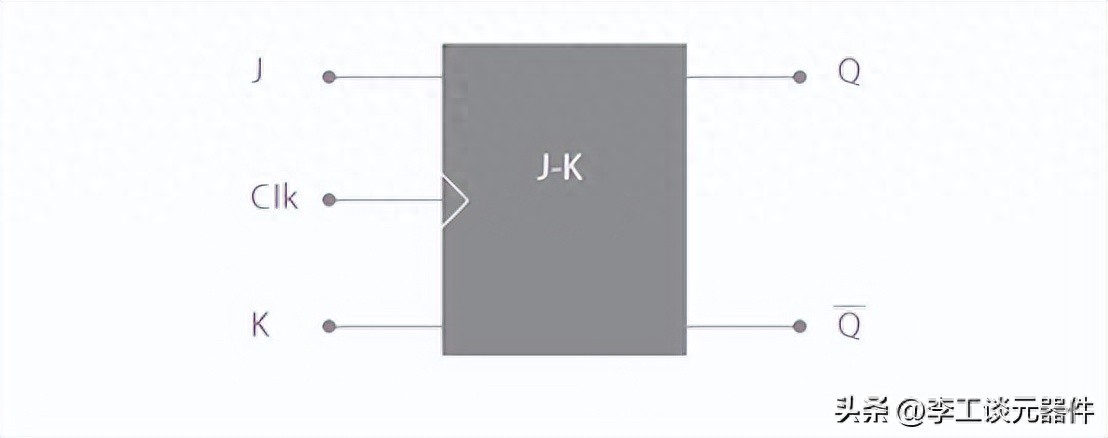

JK触发器由两个输入 J(置位)和 K(复位)、一个时钟输入以及两个表示为 Q 和 Q 的输出组成。

时钟输入用于触发触发器并改变其状态。Q是JK触发器的主输出,Q是输出Q的补码。

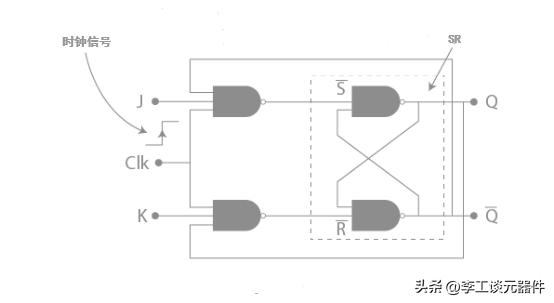

JK触发器的内部结构可以用 NAND 门锁存器来解释。与非门是一种逻辑门,产生的输出是其输入的逻辑与的补码,JK触发器由两个与非门构成,如下图所示:

输入 J 和 K 连接到第一与非门的输入,而第一与非门的输出连接到第二与非门的输入。第二个与非门的输出连接到第一个与非门的输入,也形成反馈回路(这就是它们被称为时序电路的原因)。输入时钟连接到两个与非门,其信号决定触发器的输出何时改变。

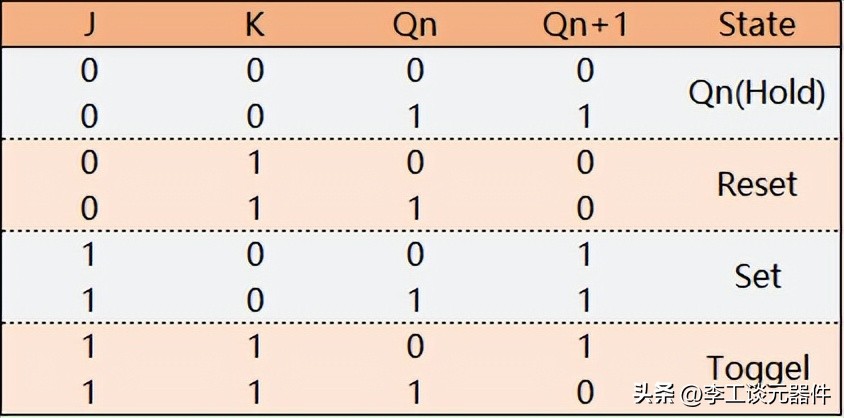

JK触发器真值表有保持状态、复位状态、置位状态和切换状态。由于这是SR触发器的细化,因此将SR触发器的真值表细化为IK触发器的真值表。

JK触发器的真值表有两个输入,J和K,Q n表示当前状态, Q n+1表示下一个状态,如下表所示:

如下:在上面的真值表中,Q(n)代表触发器在n时刻的输出,而Q(n+1)代表其在n+1时刻的输出。

。特征表有输入 J 和 K,Qn 和 Q n+1表示当前状态,表示特征表中的下一个状态,如下所示:

上述特性表中具有保持状态、复位状态、置位状态和切换状态的 JK 触发器的特性方程使用三变量 k-map 如下所示。

经过两个 NAND 门的传播延迟时间 t pd后,输出将切换至 Q n = 1。由于这是对输入的反馈,因此在另一次延迟 t pd (FF)后,输出将切换回 Q n = 0 。

只要低时钟脉冲宽度长于触发器传播延迟(t pd),这种情况就会持续下去。

电 话:0898-08980898 手 机:13877778888 传 真:0000-0000-00 E-mail:admin@Your website.com

地 址:广东省清远市

扫码关注我们